„JFET” változatai közötti eltérés

(Új oldal, tartalma: „ Az unipoláris (FET = field effect tranzisztor, térvezérlésű tranzisztor) tranzisztorok elnevezésüket onnan nyerték, hogy a tranzisztoron átfolyó áramot a vezé...”) |

a (+= kat) |

||

| 1. sor: | 1. sor: | ||

| − | |||

Az unipoláris (FET = field effect tranzisztor, térvezérlésű tranzisztor) tranzisztorok elnevezésüket onnan nyerték, hogy a tranzisztoron átfolyó áramot a vezérlőelektródájukra kapcsolt feszültséggel vezérelt villamos térrel lehet befolyásolni. | Az unipoláris (FET = field effect tranzisztor, térvezérlésű tranzisztor) tranzisztorok elnevezésüket onnan nyerték, hogy a tranzisztoron átfolyó áramot a vezérlőelektródájukra kapcsolt feszültséggel vezérelt villamos térrel lehet befolyásolni. | ||

| 87. sor: | 86. sor: | ||

A JFET drain áram - gate feszültség karakterisztikáját az 4.b.ábra mutatja. Az ábra azt az állapotot szemlélteti, amikor a csatorna (UDS feszültség hatására) már el van záródva. Up gatefeszültségnél a FET lezár, ekkor a drain áram 0. Ha UG ennél az értéknél pozitívabb, a drain áram növekszik. A gatefeszültség kb. +0,5V-ig növelhető, ennél nagyobb UG esetén a gate-source dióda kinyit, és a FET már nem működőképes. | A JFET drain áram - gate feszültség karakterisztikáját az 4.b.ábra mutatja. Az ábra azt az állapotot szemlélteti, amikor a csatorna (UDS feszültség hatására) már el van záródva. Up gatefeszültségnél a FET lezár, ekkor a drain áram 0. Ha UG ennél az értéknél pozitívabb, a drain áram növekszik. A gatefeszültség kb. +0,5V-ig növelhető, ennél nagyobb UG esetén a gate-source dióda kinyit, és a FET már nem működőképes. | ||

| + | |||

| + | [[Kategória:Elektronikai alkatrészek]] | ||

A lap 2008. október 25., 17:10-kori változata

Az unipoláris (FET = field effect tranzisztor, térvezérlésű tranzisztor) tranzisztorok elnevezésüket onnan nyerték, hogy a tranzisztoron átfolyó áramot a vezérlőelektródájukra kapcsolt feszültséggel vezérelt villamos térrel lehet befolyásolni.

Feszültséggel vezérelhető ellenállás

A záró irányban előfeszített p-n átmenet feszültséggel vezérelhető kapacitásként működik: minél nagyobb a zárófeszültség, annál szélesebb lesz a kiürített réteg, így annál távolabb kerülnek egymástól a „p” és „n” réteg szabad (többségi) töltéshordozói, ezzel mintegy nő a távolság a kondenzátor „fegyverzetei” között és ezért csökken az eszköz kapacitása.

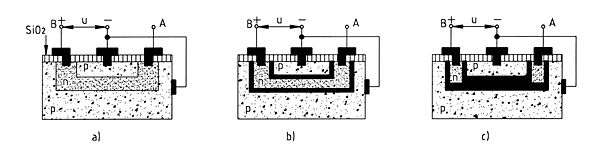

A záró irányban előfeszített p-n átmenet feszültséggel vezérelhető ellenállásként is felhasználható. Az 1. ábrán látható eszközben két „p” réteg között egy „n” réteg helyezkedik el, a két „p” rétegen, valamint az „n” réteg (az un. csatorna = channel) két végpontján (A és B) rezisztív kivezetéseket helyeztek el. A két „p” réteghez tartozó kivezetéseket összekötve, ezek képezik a vezérlő elektródát („kapu” = gate). A vezérelhető ellenállás a csatorna „A” és „B” végpontja közt jelentkezik.

- 1. ábra: Feszültséggel vezérelhető ellenállás

Ha a vezérlő elektródára „A” ponthoz képest 0 feszültséget adunk, a p-n átmeneteken csekély szélességű kiürített réteg alakul ki, ezért a csatorna szabad keresztmetszete viszonylag nagy, két végpontja közötti ellenállás pedig kicsi (1.a. ábra).

A vezérlő elektródára kis zárófeszültséget kapcsolva, a kiürített réteg szélessége megnő, a csatorna keresztmetszete csökken, ezért ellenállása megnő (1.b. ábra).

A vezérlő elektródára kapcsolt zárófeszültséget növelve a kiürített réteg egyre szélesedik, és egy, az eszközre jellemző Up vezérlő feszültségnél már a csatorna teljes keresztmetszetét elzárja (1.c. ábra). Ekkor „A” és „B” pont között nem folyhat áram, az ellenállás gyakorlatilag végtelen (a csatorna elzáródott).

A csatorna ellenállását tehát a vezérlő elektródára kapcsolt feszültséggel lehet változtatni; a vezérlő feszültség a kiürített réteg szélességét befolyásolja. Célszerű, ha a kiürített réteg inkább az ellenállást képező csatornába nyúlik be, ezért gyártáskor a csatornát igen gyengén, míg a vezérlő elektródát erősen adalékolják.

Az eszköz jellegzetes lezáró feszültsége Up= 1...7V, a csatorna ellenállása pedig a 0 vezérlő feszültségnél érvényes kb. 100 Ω-tól több MΩ-ig (elzáródáskor) terjedhet.

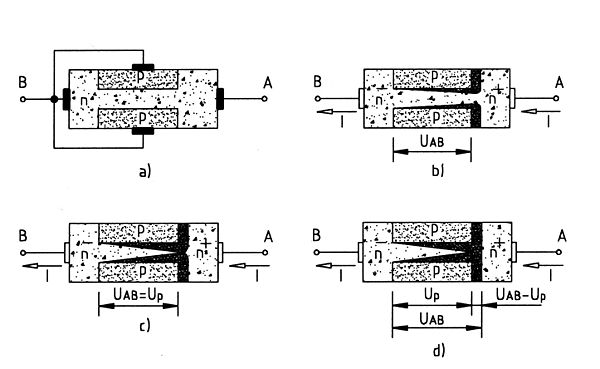

Ha a csatornán áram folyik, a csatorna ellenállásán feszültség esik. Ha ez a feszültség nem hanyagolható el az elzáródáshoz tartozó Up feszültséghez képest, a csatorna mentén a feszültség „A” és „B” pont között változik, ennek megfelelően változik a csatorna és a vezérlő elektróda közti lezáró feszültség is. A folyamatot a 2. ábrán követhetjük.

- 2. ábra

A 2.a. ábra azt az állapotot mutatja, amikor (0 gate feszültség mellett) az ellenálláson nem folyik áram.

A 2.b. ábrán látható, hogy ha a csatornára UAB < Up feszültséget kapcsolnak, az eszközön áram indul meg, a csatorna mentén eső UAB feszültség miatt a kiürített réteg a csatorna mentén változó szélességű.

Amikor az eszközre kapcsolt UAB feszültség eléri Up értéket, a csatorna elzáródik (2.c. ábra). Ez a pont felel meg a 2.e. ábra szerinti görbe állandó áramú tartománya kezdetének.

Ha a csatornára kapcsolt UAB feszültség nagyobb, mint Up lezárófeszültség, a kiürített réteg és az elzáródott tartomány a 2.d. ábra szerint az eszköz jobb oldala felé terjeszkedik, elszigetelve a csatornát az „A” kivezetéstől. Ezért a kívülről rákapcsolt feszültség növekedése nem befolyásolja már a csatorna elzáródását, tehát a csatorna áramát sem: az átfolyó áram stabilizálódik (2.e. ábra állandó áramú tartomány).

Ilyen formán az eszköz mint áramstabilizátor használható.

A feszültséggel vezérelhető ellenállás az elzáródás miatt lineáris elemként kevéssé használható, viszont a térvezérlésű tranzisztor alapját képezi.

Feszültséggel vezérelhető ellenállás természetesen nem csak a tárgyalt „n csatornás”, hanem „p csatornás” kivitelben is készíthető, amikor is a vezérlő elektródát képező két „n” réteg fogja közre a „p” típusú csatornát.

Záróréteges térvezérlésű tranzisztor (Junction FET = JFET)

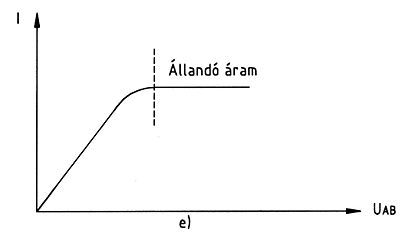

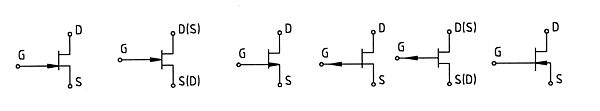

Az záróréteges térvezérlésű tranzisztor felépítésében azonos a feszültséggel vezérelhető ellenállással. A FET vezérlő elektródáját (amely a tranzisztor bázisának felel meg) gate-nek (G, kapu) nevezik, a csatorna kivezetései pedig a tranzisztor emitterének megfelelő source (S, forrás) illetve a tranzisztor kollektorának megfelelő drain (D, nyelő). A JFET rajzjelét a 3. ábra mutatja.

- 3.ábra

- a) n-channel JFET___________________________b) p-channel JFET

A csatorna típusát a nyíl irányával szemléltetik: „n” csatornás JFET esetében a (source elektródával szemközti) gate elektródára a csatorna felé mutató nyíl kerül (jelölve, hogy a gate a „p”, a csatorna pedig az „n” típusú), vagy ezzel azonos jelentésű, ha a source elektródára egy az előzővel azonos irányítású, tehát kifelé mutató nyilat rajzolnak (3.a. ábra).

A „p” csatornás JFET rajzjelén a gate-ra rajzolt nyíl kifelé, vagy a source-ra rajzolt nyíl befelé mutat (3.b. ábra).

A gate és a drain feszültségét a source-hoz képest mérik. A JFET működéséhez az szükséges, hogy a gate záró irányban legyen előfeszítve (vagy legalább is a nyitóirányú előfeszültsége kisebb legyen, mint az adott félvezető anyagra jellemző kontaktpotenciál, azaz szilícium esetén kb.0,5V), pl. n csatornás FET esetén a source-hoz képest negatív vagy legfeljebb +0,5V legyen.

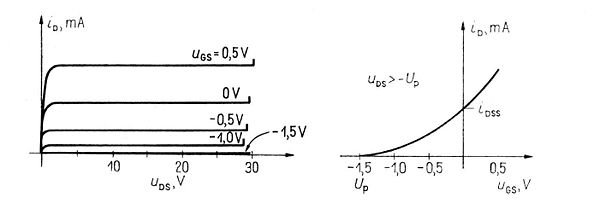

Ha a gatefeszültség 0, akkor az eszköz és működése ugyanaz, mint az előző pontban tárgyalt feszültséggel vezérelhető ellenállásé (ld. 4. ábra UGS=0V görbe). Ameddig UDS drain-source feszültség nem éri el Up feszültséget, az eszköz (nem teljesen lineáris) ellenállásként viselkedik, azaz a drain-source feszültség növekedésekor a drain áram is nő. Up drainfeszültség elérésekor a csatorna lezáródik, ettől kezdve a drain áram nem nő tovább UDS növelésekor.

- 4. ábra: n csatornás JFET karakterisztikái

Ha a gatefeszültség negatív pl. -0,5V értékű, a csatornában a kiürített réteg kiszélesül, a csatorna keresztmetszete csökken, ezért ellenállása megnő, és azonos UDS feszültség hatására kisebb áram folyhat, mint UGS=0V esetén. A drain-source feszültség növelésekor a csatorna mentén a kiürített réteg tovább terjeszkedik, így a csatorna keresztmetszete tovább csökken. Mivel a negatív gate-source feszültség miatt a csatorna már UDS=0 esetén is részben el volt zárva, a teljes elzáródáshoz most kevesebb UDS feszültség tartozik.

Még negatívabb gatefeszültségnél a csatorna nagyobb elzáródása miatt még kisebb draináram alakul ki azonos UDS feszültség esetén, illetve a csatorna teljes elzáródása még kisebb UDS feszültségnél következik be.

A JFET drain áram - gate feszültség karakterisztikáját az 4.b.ábra mutatja. Az ábra azt az állapotot szemlélteti, amikor a csatorna (UDS feszültség hatására) már el van záródva. Up gatefeszültségnél a FET lezár, ekkor a drain áram 0. Ha UG ennél az értéknél pozitívabb, a drain áram növekszik. A gatefeszültség kb. +0,5V-ig növelhető, ennél nagyobb UG esetén a gate-source dióda kinyit, és a FET már nem működőképes.